- 您现在的位置:买卖IC网 > Sheet目录3878 > PIC16F639-E/SO (Microchip Technology)IC MCU FLASH 2KX14 20SOIC

Micrel, Inc.

KSZ8841-PMQL

October 2007

26

M9999-100407-1.5

The following table shows the RDES1 register bit fields.

Bit

Description

31 - 26

Reserved

25

RER Receive End of Ring

When set, indicates that the descriptor list reached its final descriptor. The KSZ8841-PMQL

returns to the base address of the list, thus creating a descriptor ring.

24 - 12

Reserved

10 - 0

RBS Receive Buffer Size

Indicates the size, in bytes, of the receive data buffer. If the field is 0, the KSZ8841-PMQL

ignores this buffer and moves to the next descriptor.

The buffer size must be a multiple of 4.

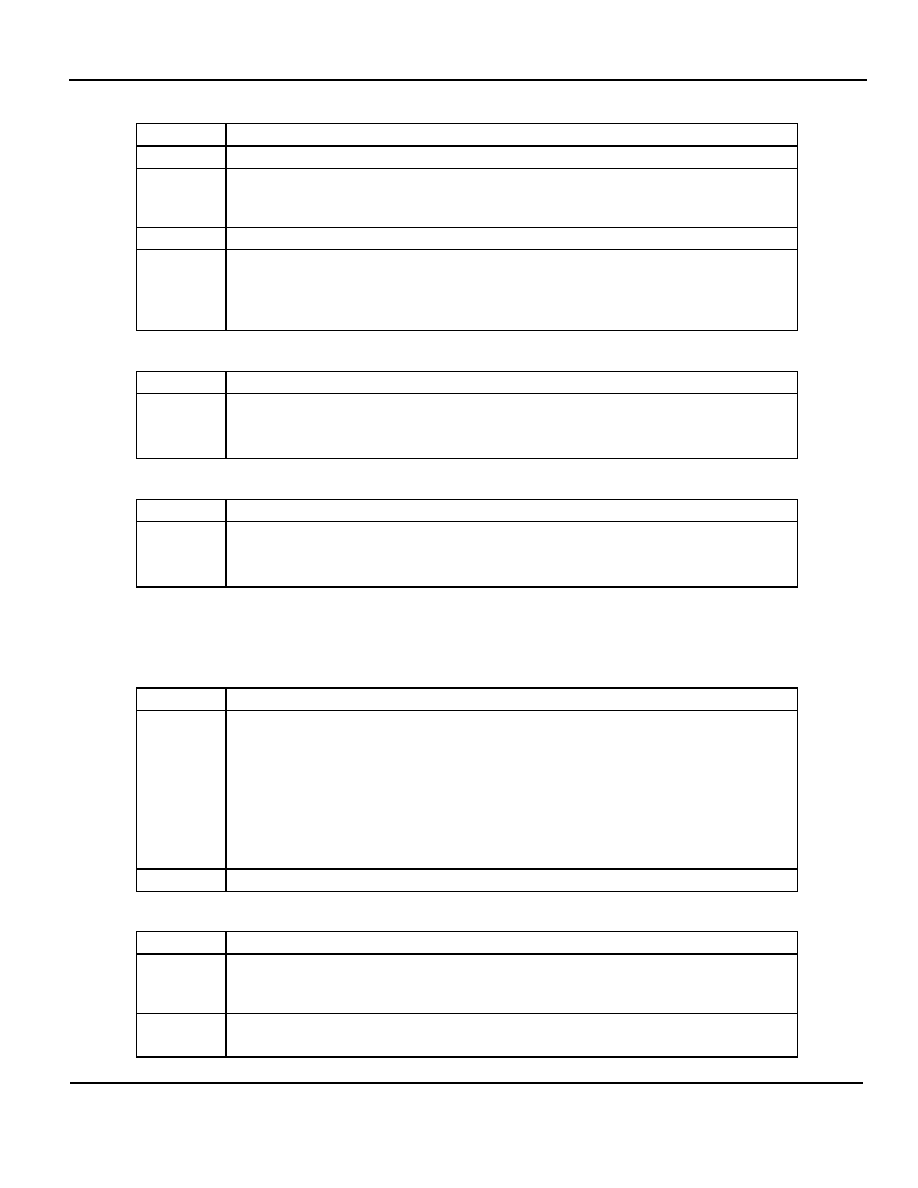

The following table shows the RDES2 register bit fields.

Bit

Description

31 - 0

Buffer Address

Indicates the physical memory address of the buffer.

The buffer address must be Word aligned.

The following table shows the RDES3 register bit fields.

Bit

Description

31 - 0

Next Descriptor Address

Indicates the physical memory address of the next descriptor in the descriptor ring.

The buffer address must be Word aligned.

Transmit Descriptors (TDES0-TDES3)

Transmit descriptors must be Word aligned. Each descriptor provides one frame buffer, one byte count field, and

control and status bits.

The following table shows the TDES0 register bit fields.

Bit

Description

31

OWN Own Bit

When set, indicates that the descriptor is owned by the KSZ8841-PMQL. When cleared,

indicates that the descriptor is owned by the host. The KSZ8841-PMQL clears this bit either

when it completes the frame transmission or when the buffer allocated in the descriptor is

empty.

The ownership bit of the first descriptor of the frame should be set after all subsequent

descriptors belonging to the same frame have been set. This avoids a possible race

condition between the KSZ8841-PMQL fetching a descriptor and the driver setting an

ownership bit.

30 - 0

Reserved

The following table shows the TDES1 register bit fields.

Bit

Description

31

IC Interrupt on Completion

When set, the KSZ8841-PMQL sets transmit interrupt after the present frame has been

transmitted. It is valid only when last segment is set.

30

FS First Segment

When set, indicates that the buffer contains the first segment of a frame.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24F08KL402-I/SS

IC MCU 16BIT 8KB FLASH 28-SSOP

PIC16F1936-I/MV

IC MCU 8BIT 14KB FLASH 28UQFN

PIC16LF724-I/PT

IC PIC MCU FLASH 7KB 44-TQFP

PIC16F724-I/MV

MCU 7KB FLASH PROGRAM 40-UQFN

PIC16LF724-I/MV

MCU PIC 7KB FLASH XLP 40-UQFN

PIC18F2331T-I/SO

IC MCU FLASH 4KX16 28SOIC

PIC16LF873AT-I/SOG

IC MCU FLASH 4KX14 28SOIC

PIC16LF819T-I/SOG

IC MCU FLASH 2KX14 18SOIC

相关代理商/技术参数

PIC16F639-E/SS

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/P

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/SO

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/SS

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639-I/SS

制造商:Microchip Technology Inc 功能描述:8-Bit Microcontroller IC

PIC16F639T-I/SO

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F639T-I/SS

功能描述:8位微控制器 -MCU 4kb 128 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F648A-E/ML

功能描述:8位微控制器 -MCU 7KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT